II. Rolling Monthly

The present targets for the Total and Cold times are:

Total time per SI Mode per measurement: 7600.0 seconds

Fraction of total time the measurement should be cold: 60.0%

Back To Top

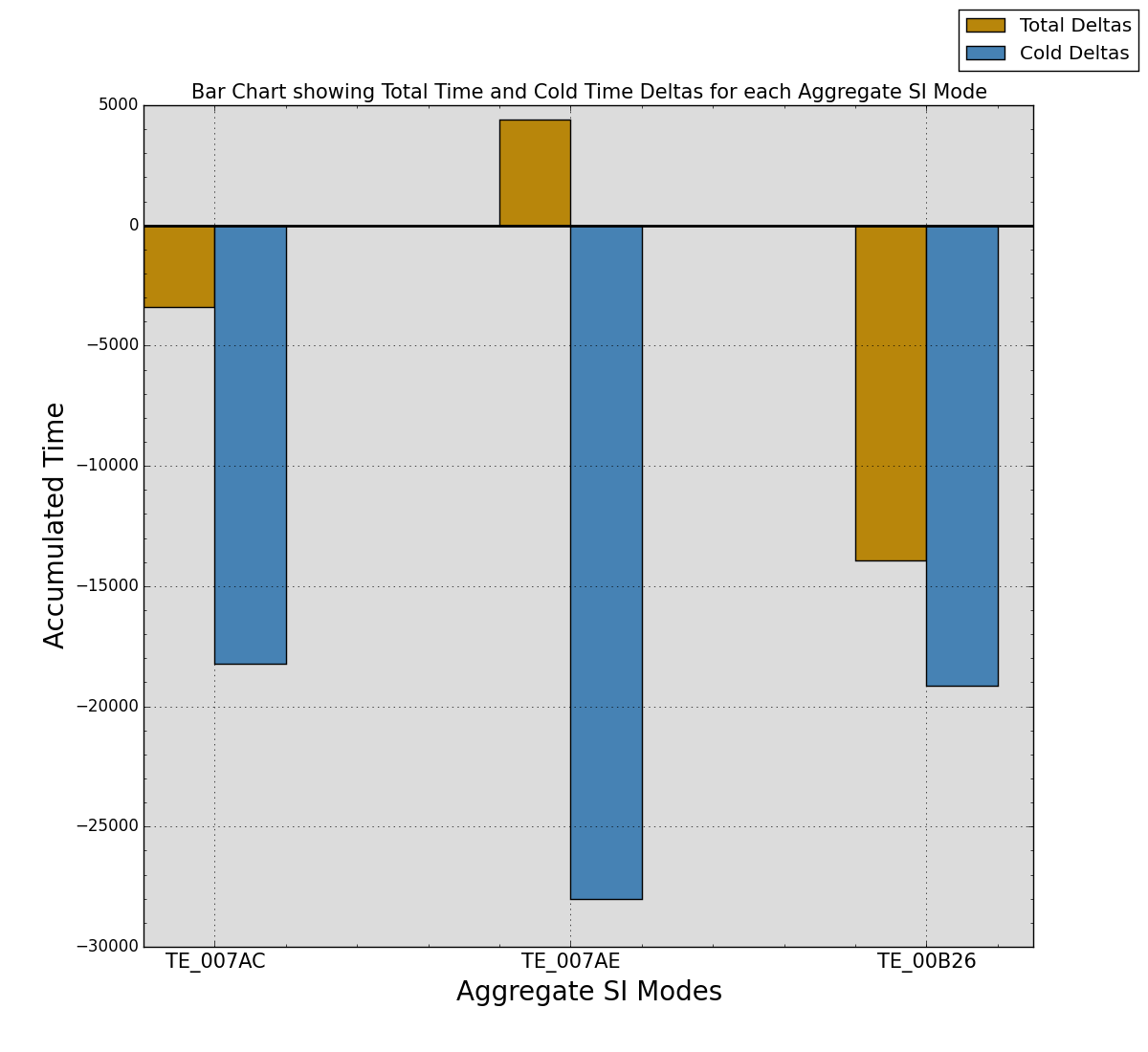

| Stats | TE_007AC | TE_007AE | TE_00B26 |

|---|---|---|---|

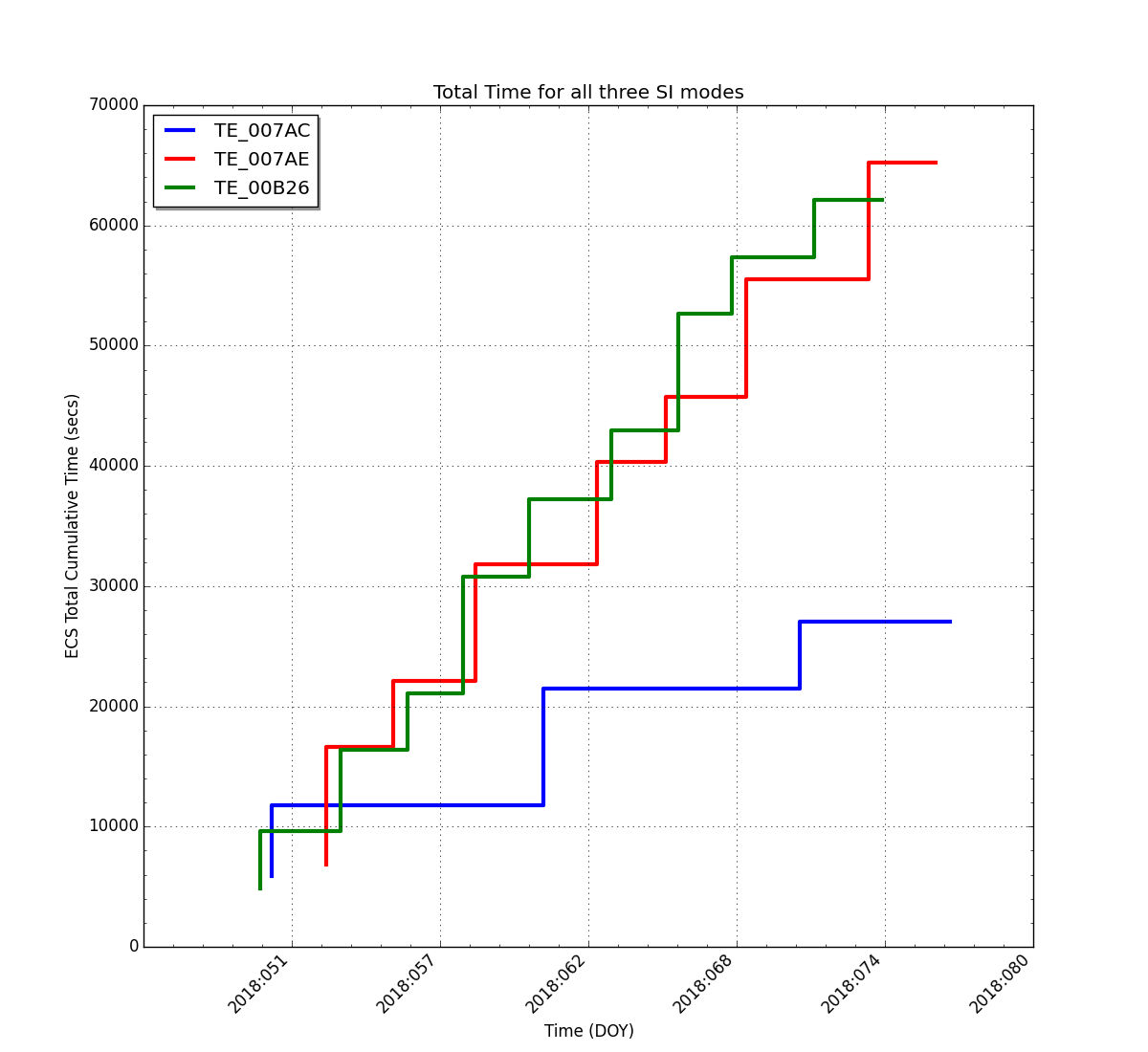

| Total Expected Time (secs) | 30400 | 60800 | 76000 |

| Total Actual Time (secs) | 27013 | 65206 | 62087 |

| Delta From Expected (secs) | -3387.00 | 4406.00 | -13912.00 |

| % of Expected Total (secs) | 88.86% | 107.25% | 81.69% |

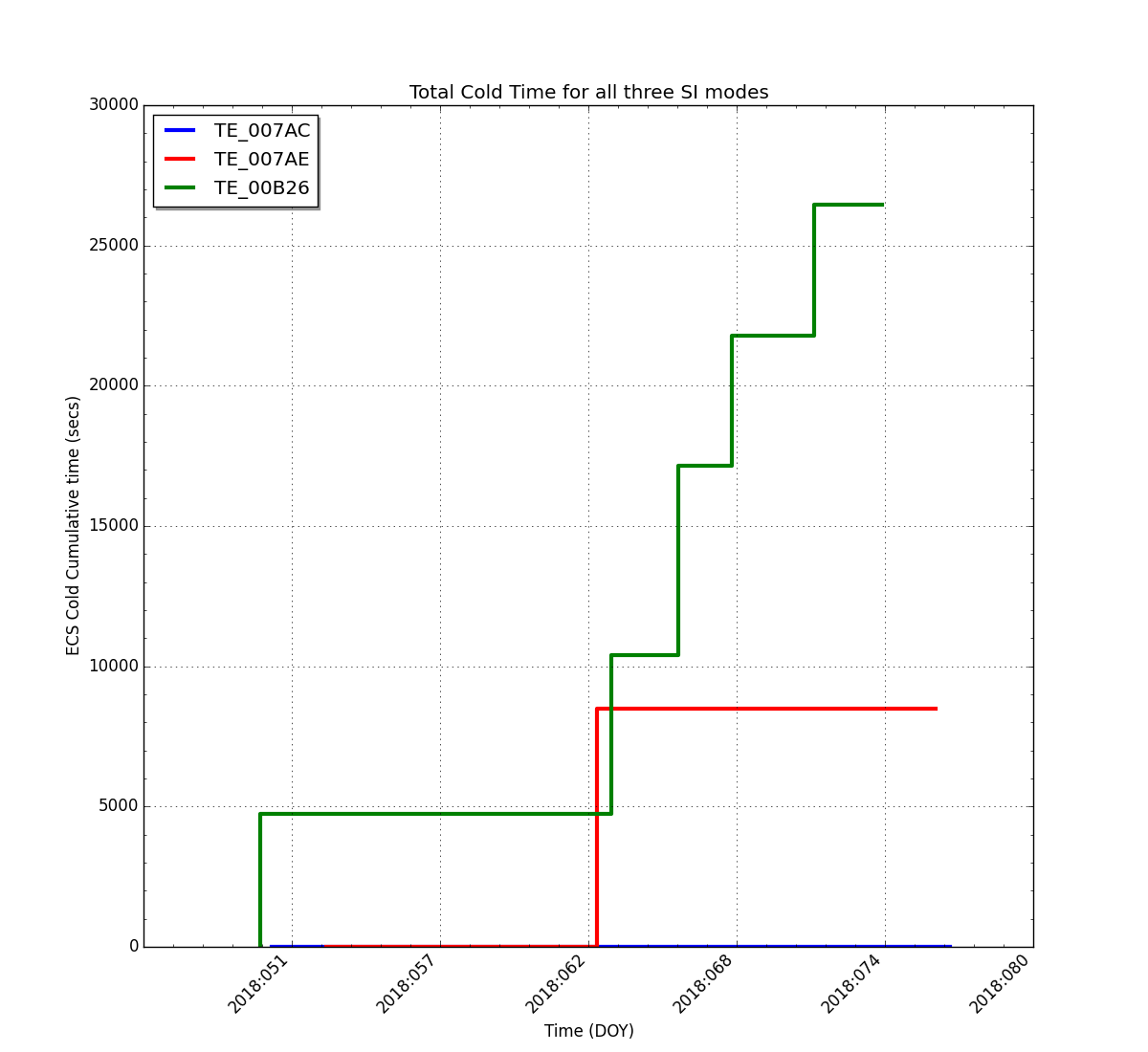

| Stats | TE_007AC | TE_007AE | TE_00B26 |

|---|---|---|---|

| Total Exp. Cold Time (secs) | 18240.0 | 36480.0 | 45600.0 |

| Total Actual Cold Time (secs) | 0 | 8474 | 26466 |

| Delta From Expected (secs) | -18240.00 | -28005.30 | -19133.73 |

| % of Exp. Cold Total (secs) | 0.00% | 23.23% | 58.04% |

| SI Mode | Total Number of Obs. | Total Exposure Time (sec) | Average Exposure (sec/obs) | |

|---|---|---|---|---|

| Primary 6 Chip SI Modes | TE_007AC | 4 | 27013.00 | 6753.25 |

| TE_007AE | 5 | 36055.00 | 7211.00 | |

| TE_00B26 | 9 | 57371.00 | 6374.56 | Old 6 Chip SI Modes | TE_00216 | 0 | 0.00 | 0.00 |

| TE_0021C | 0 | 0.00 | 0.00 | |

| TE_008EA | 0 | 0.00 | 0.00 | 5 Chip SI Modes | TE_00C60 | 1 | 4717.00 | 4717.00 |

| TE_00CA8 | 3 | 29151.00 | 9717.00 | 4 Chip SI Modes | TE_00C62 | 0 | 0.00 | 0.00 |

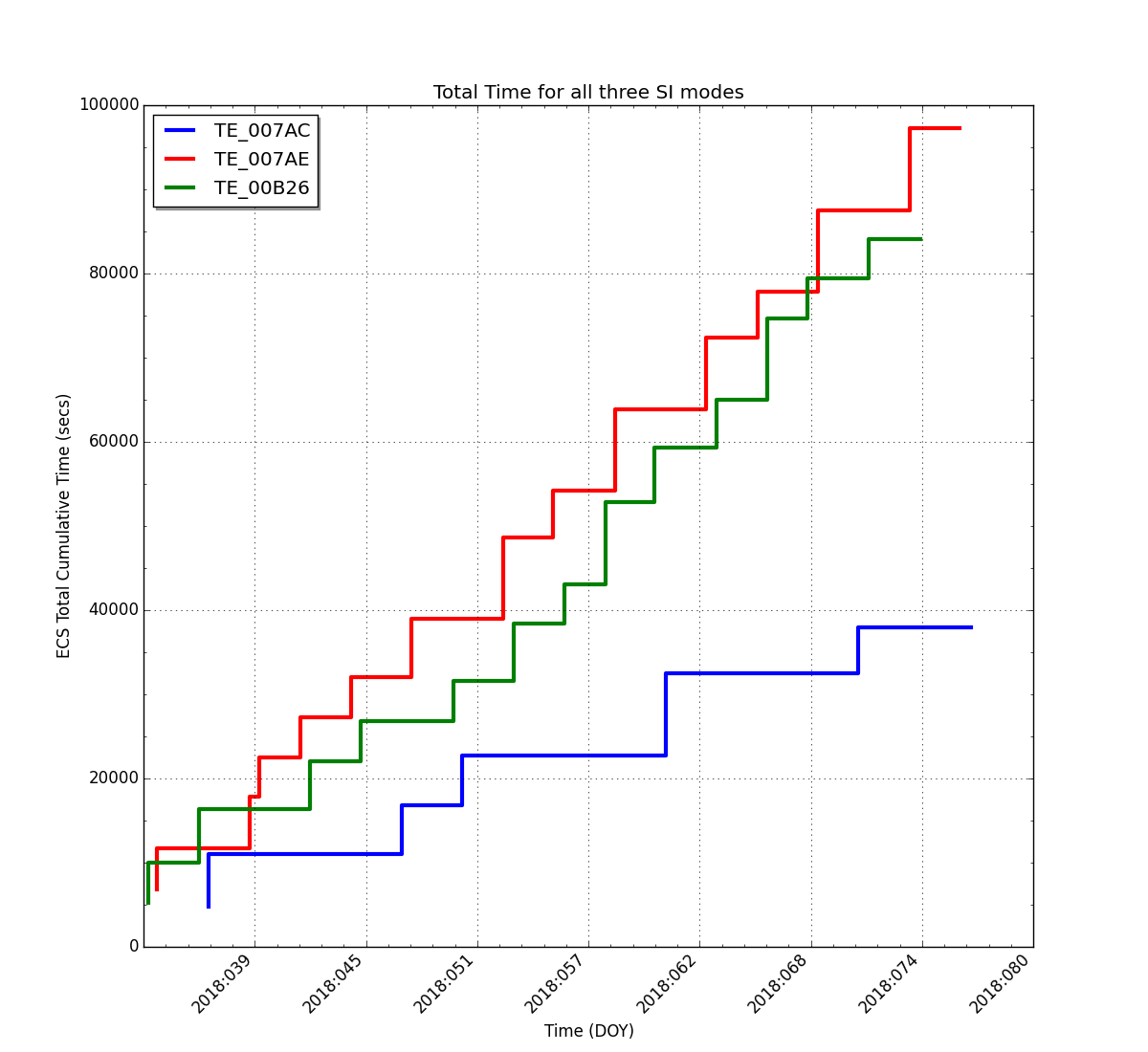

III. Statistics Since the Start of the Current Epoch

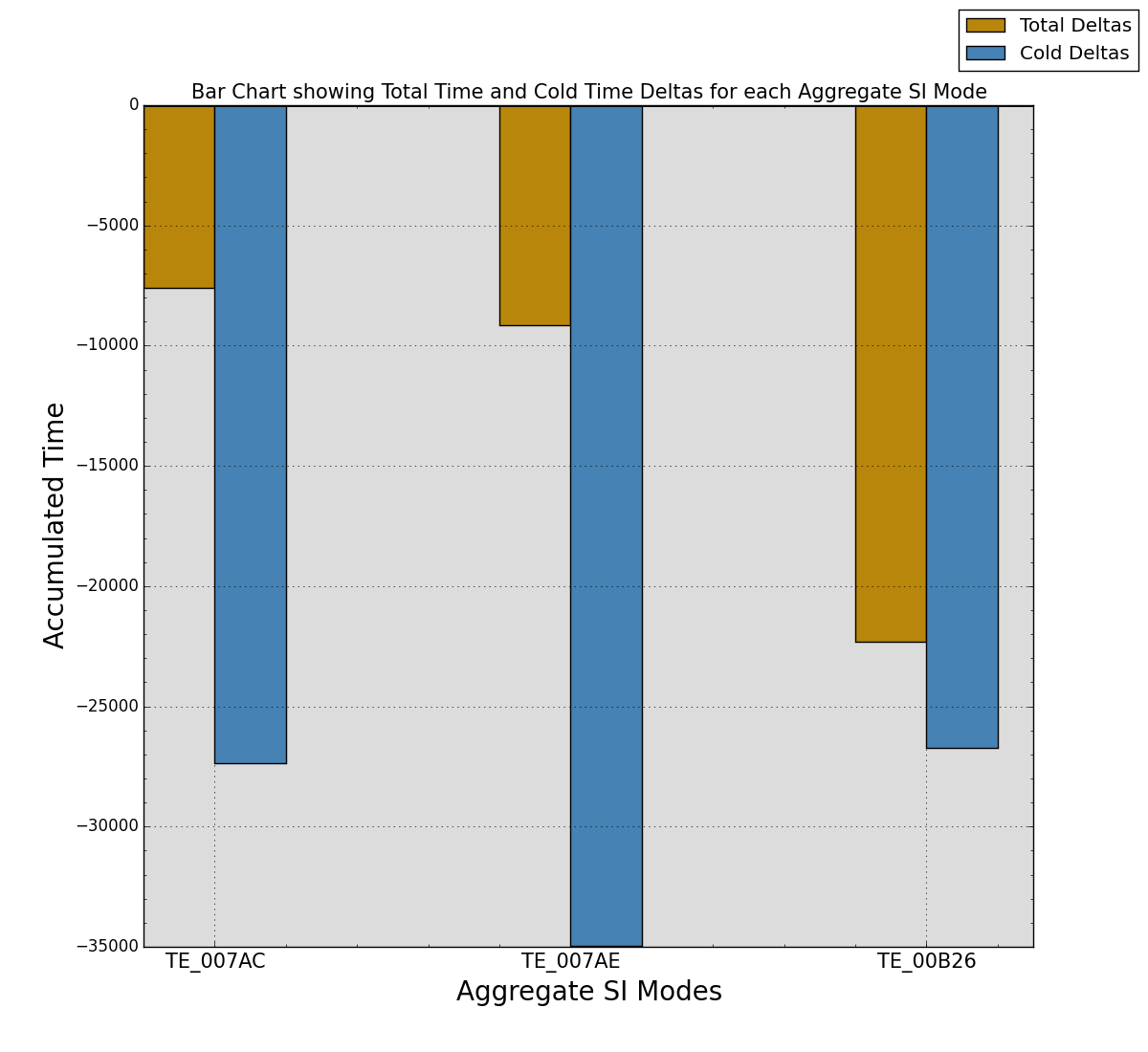

| Stats | TE_007AC | TE_007AE | TE_00B26 |

|---|---|---|---|

| Total Expected Time (secs) | 45600 | 106400 | 106400 |

| Total Actual Time (secs) | 38001 | 97271 | 84095 |

| Delta From Expected (secs) | -7599.00 | -9129.00 | -22304.00 |

| % of Expected Total (secs) | 83.34% | 91.42% | 79.04% |

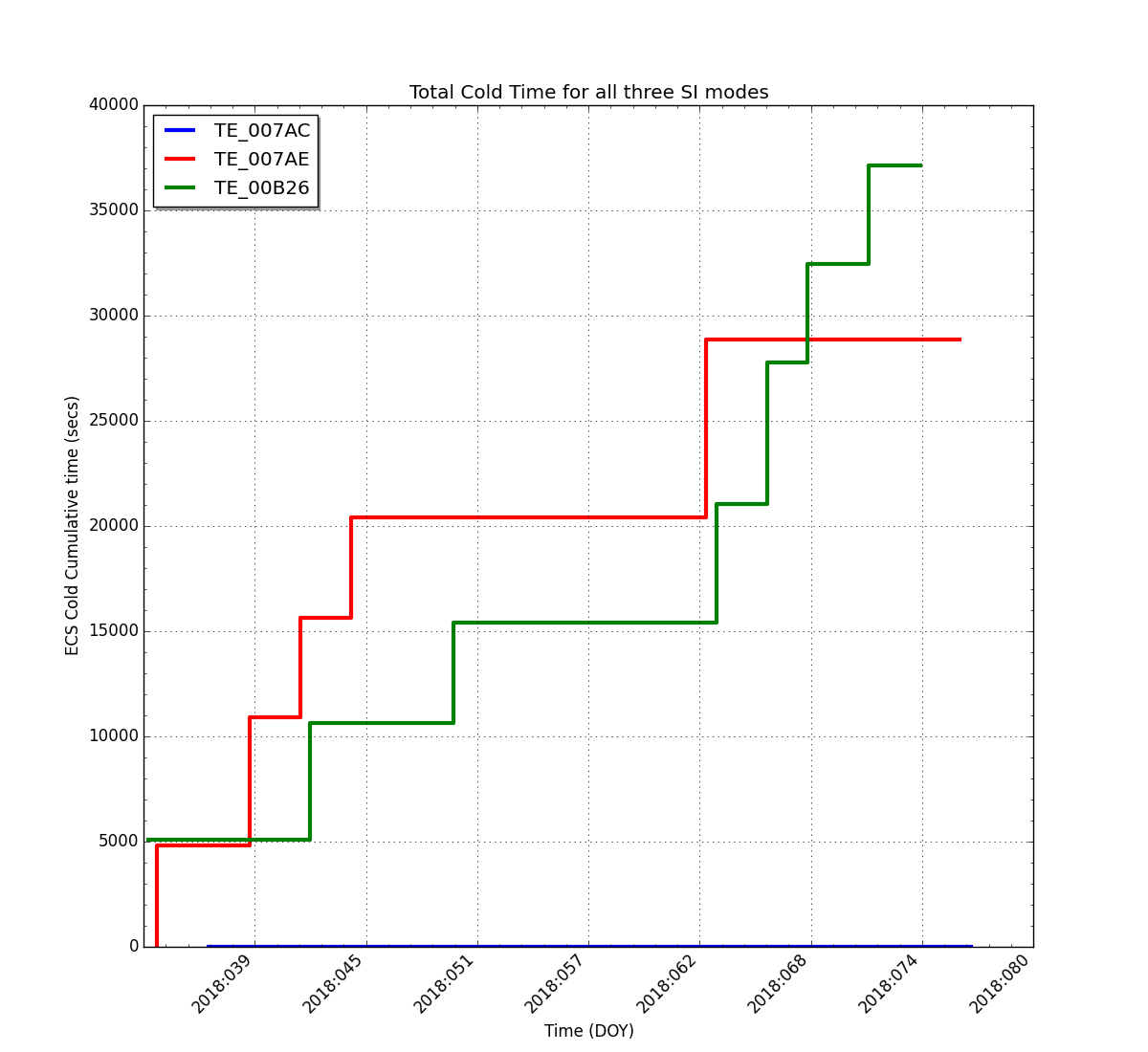

| Stats | TE_007AC | TE_007AE | TE_00B26 |

|---|---|---|---|

| Total Exp. Cold Time (secs) | 27360.0 | 63840.0 | 63840.0 |

| Total Actual Cold Time (secs) | 0 | 28871 | 37115 |

| Delta From Expected (secs) | -27360.00 | -34968.82 | -26724.49 |

| % of Exp. Cold Total (secs) | 0.00% | 45.22% | 58.14% |

| SI Mode | Total Number of Obs. | Total Exposure Time (sec) | Average Exposure (sec/obs) | |

|---|---|---|---|---|

| Primary 6 Chip SI Modes | TE_007AC | 6 | 38001.00 | 6333.50 |

| TE_007AE | 10 | 63289.00 | 6328.90 | |

| TE_00B26 | 13 | 79379.00 | 6106.08 | Old 6 Chip SI Modes | TE_00216 | 0 | 0.00 | 0.00 |

| TE_0021C | 0 | 0.00 | 0.00 | |

| TE_008EA | 0 | 0.00 | 0.00 | 5 Chip SI Modes | TE_00C60 | 1 | 4717.00 | 4717.00 |

| TE_00CA8 | 4 | 33982.00 | 8495.50 | 4 Chip SI Modes | TE_00C62 | 0 | 0.00 | 0.00 |

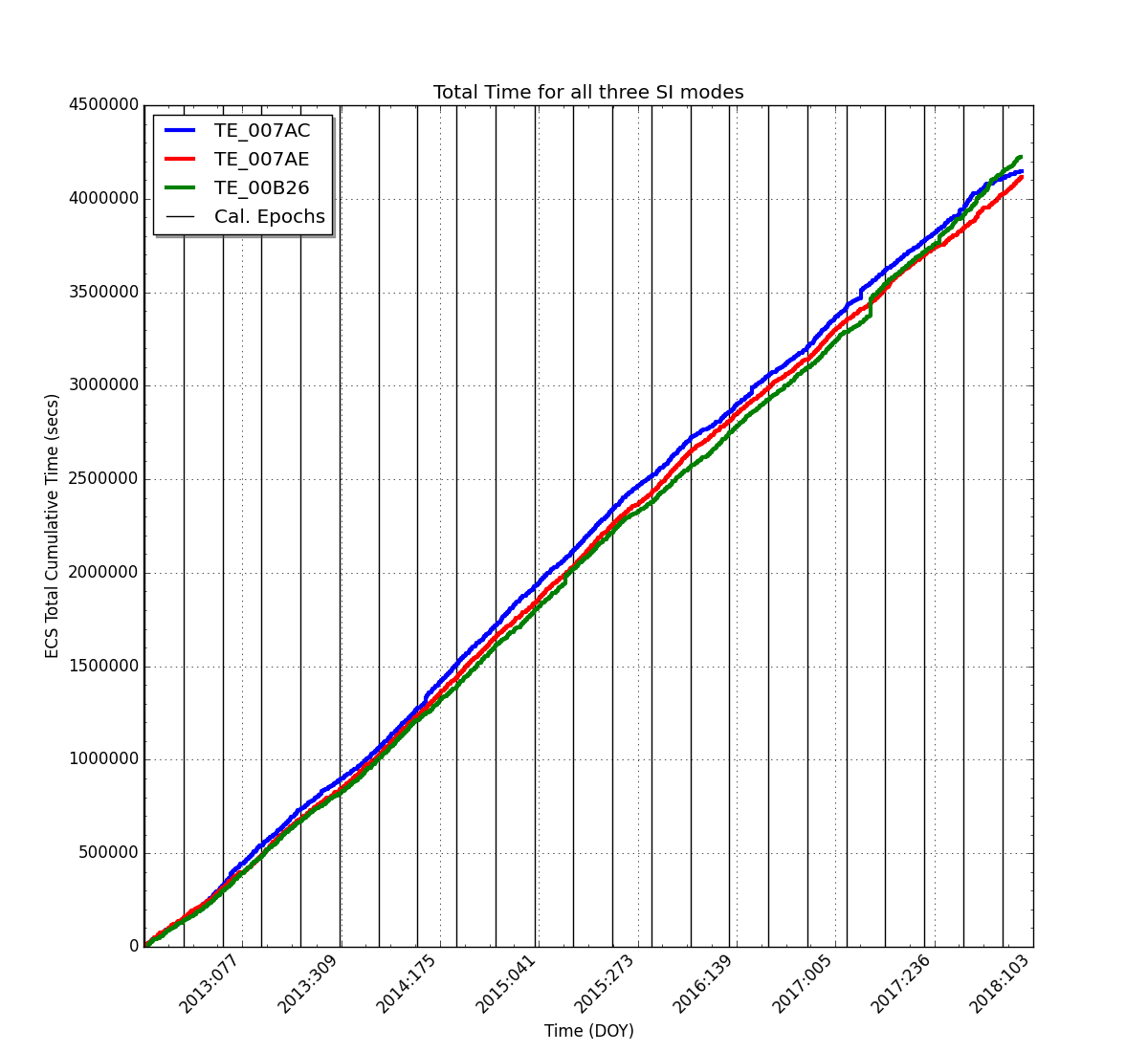

| Stats | TE_007AC | TE_007AE | TE_00B26 |

|---|---|---|---|

| Total Expected Time (secs) | 3800000 | 3838000 | 3853200 |

| Total Actual Time (secs) | 4146095 | 4114547 | 4223434 |

| Delta From Expected (secs) | 346095.52 | 276547.04 | 370234.65 |

| % of Expected Total (secs) | 109.11% | 107.21% | 109.61% |

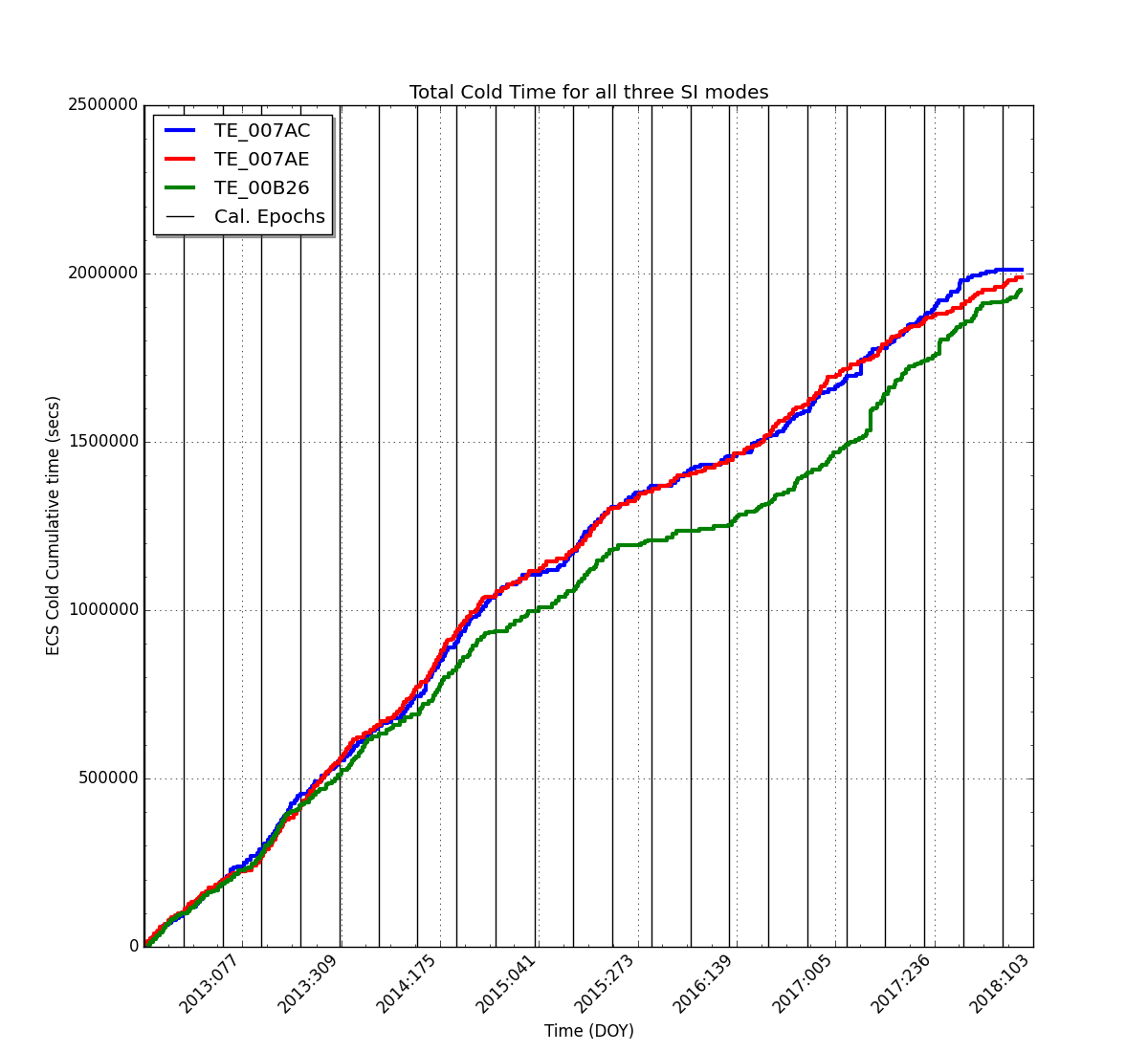

| Stats | TE_007AC | TE_007AE | TE_00B26 |

|---|---|---|---|

| Total Exp. Cold Time (secs) | 2280000.0 | 2302800.0 | 2311920.0 |

| Total Actual Cold Time (secs) | 2012159 | 1989097 | 1950493 |

| Delta From Expected (secs) | -267840.84 | -313702.06 | -361426.89 |

| % of Exp. Cold Total (secs) | 88.25% | 86.38% | 84.37% |

| SI Mode | Total Number of Obs. | Total Exposure Time (sec) | Average Exposure (sec/obs) | |

|---|---|---|---|---|

| Primary 6 Chip SI Modes | TE_007AC | 492 | 4042012.52 | 8215.47 |

| TE_007AE | 494 | 4022319.04 | 8142.35 | |

| TE_00B26 | 498 | 4047061.92 | 8126.63 | Old 6 Chip SI Modes | TE_00216 | 5 | 478338.25 | 95667.65 |

| TE_0021C | 0 | 0.00 | 0.00 | |

| TE_008EA | 0 | 0.00 | 0.00 | 5 Chip SI Modes | TE_00C60 | 14 | 112929.00 | 8066.36 |

| TE_00CA8 | 11 | 92228.00 | 8384.36 | 4 Chip SI Modes | TE_00C62 | 3 | 167526.73 | 55842.24 |

A word about the COLD Time stats:

- The Total Expected Cold Time value in the table below is 60.0% of the Total Expected Time (see Table above).

- Total Actual Cold Time is the sum of all time during each measurement where the temperature was <= -118.7 degrees C

- % of Expected Total is the fraction of the Total Expected Time achieved

SI Mode Mapping between 6,5 and 4 chip modes:

The 6 chip SI Modes consist of three distinct modes. But there are only 2, 5 chip SI Modes and only one 4 chip SI mode. To make tracking feasible, the 4 and 5 chip modes were mapped into the 6 chip modes in the following manner:

6 chip 5 chip 4 chip

TE_007AC -> TE_00C60 TE_00C62

TE_00B26 -> TE_00C60 TE_00C62

TE_007AE -> TE_00CA8

All of the TE_00CA8s get counted as TE_007AE

Half of the TE_00C60s get counted towards TE_007AC and the other half get counted with the TE_00B26s

Half of the TE_00C62s get counted towards TE_007AC and the other half get counted with the TE_00B26s.

So watchout for TE_00B26 over-representation.

Back To Top