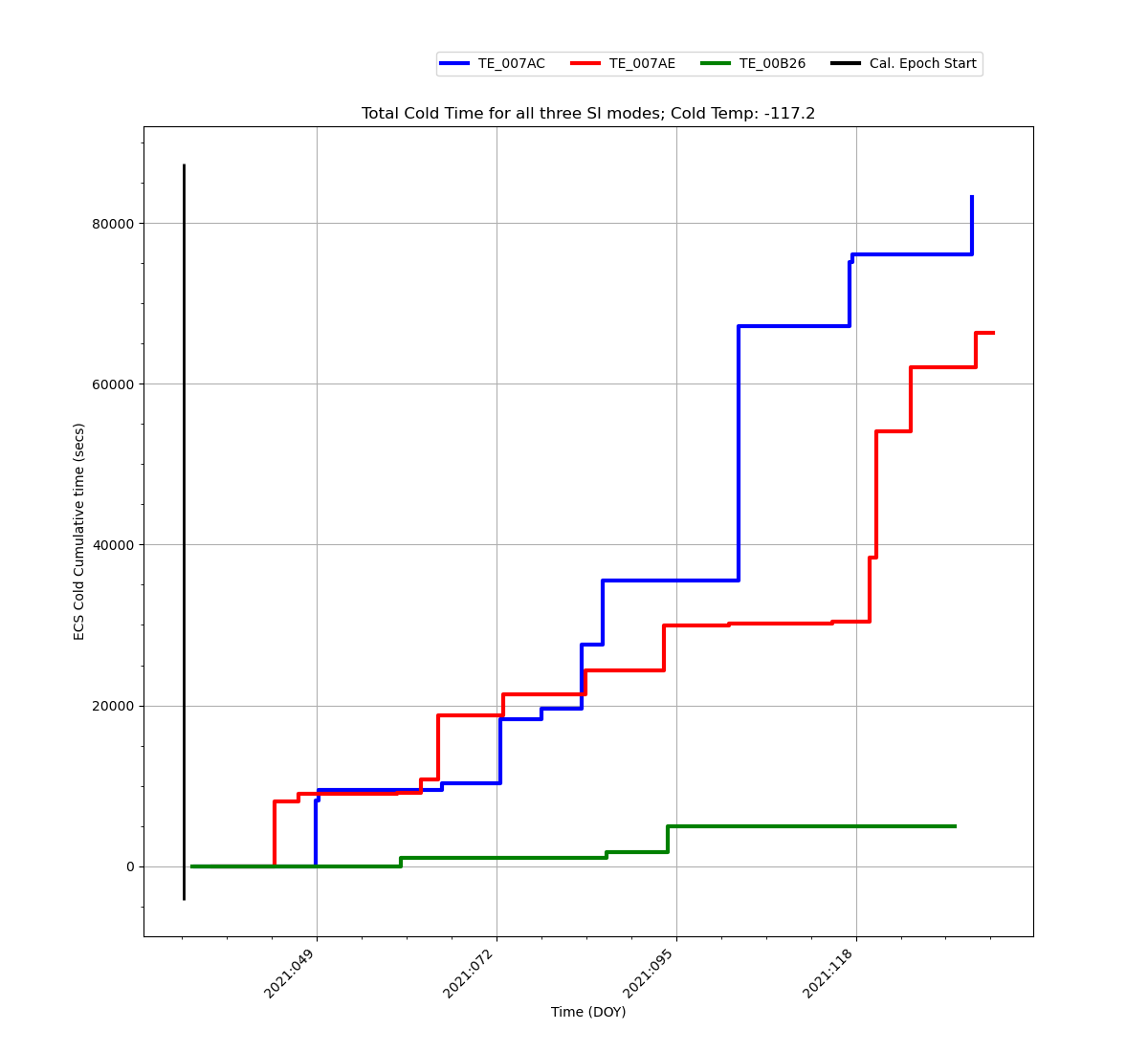

Cold time is defined as any temperature reading <= -117.2 degrees C.

NOTE: Cold Temperature Limit value changed as of the April 12, 2021 run.

We are operating on 6 month epochs. The epochs start on the following Days of the Year:

DOY 032 and DOY 213.

The present epoch begins at: 2021:032:00:00:00.00 and today is: 2021:137:11:58:06.235 .

It is important to note that the target exposure times listed below will increase by a factor

of 12% every 6 month epoch due to the half-life of the calibration source.

II. Statistics Since the Start of the Current Epoch

Cold Time Statistics:

| Chip | Required (seconds) | Achieved (seconds) |

|---|---|---|

| I0 | 160000.0 | 78784.3 |

| I1 | 160000.0 | 88240.7 |

| I2 | 160000.0 | 88240.7 |

| I3 | 160000.0 | 88240.7 |

| S0 | 80000.0 | 66361.9 |

| S1 | 100000.0 | 71271.5 |

| S2 | 160000.0 | 140236.6 |

| S3 | 200000.0 | 154602.6 |

| S4 | 80000.0 | 66361.9 |

| S5 | 80000.0 | 66361.9 |

| Recovered Science Time (seconds): | 32088.0 |

|---|

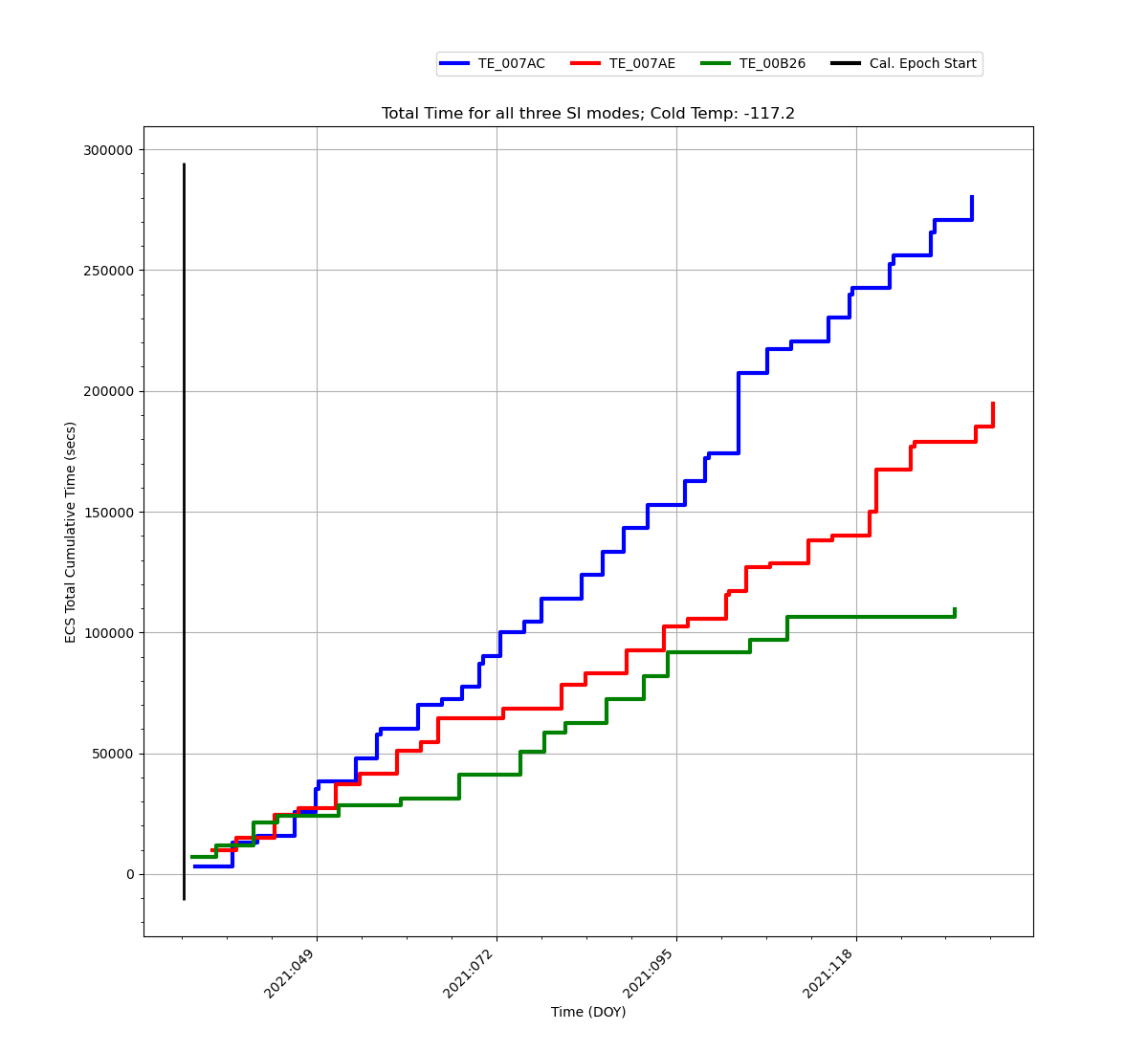

| SI Mode | Total Number of Obs. | Total Exposure Time (sec) | Average Exposure (sec/obs) | Primary 6 Chip SI Modes | TE_007AC | 24 | 185165.0 | 7715.2 |

|---|---|---|---|

| TE_007AE | 23 | 163519.20 | 7109.53 |

| TE_00B26 | 16 | 109690.00 | 6855.62 | Old 6 Chip SI Modes | TE_00216 | 0 | 0.00 | 0.00 |

| TE_0021C | 0 | 0.00 | 0.00 |

| TE_008EA | 0 | 0.00 | 0.00 | 5 Chip SI Modes | TE_00C60 | 6 | 53423.00 | 8903.83 |

| TE_00CA8 | 4 | 31283.00 | 7820.75 | 4 Chip SI Modes | TE_00C62 | 5 | 41884.40 | 8376.88 | Totals: | 78 | 584964.60 | 7499.55 |

Rule #1: The key time period for balancing SI mode statistics is the 6 month Epoch

By the end of the epoch, the SI mode statistics should match the rules stated below.

Rule #2: Each of the three, default, 6 chip, SI modes (or their 5 chip equivalents) must be used

at least once in each load week.

- If two SI modes are lagging in either cold time or total time, apportion the week's ECS

measurements between the two of them roughly commensurate with the amount they are lagging.

- The 6 month Epoch allows "even" correction of two lagging SI modes. No

need to pile a weeks worth of ECS measurements on one SI mode if two are lagging.

Rule #3: Make certain to spread the amount of COLD ECS time as evenly as possible across all three SI modes

Balance Cold measurement data between the three default 6-chip modes within 10%

of each other on an Epoch basis

Rule #4: Spread the amount of *Total* ECS time as evenly as possible across all three SI modes.

- Balance Total measurement data between the three default 6-chip modes within 10%

of each other on an Epoch basis.

Rule #3 takes precedence over Rule #4.

Rule #5:At least 60% of scheduled ECS measurement time must be -119.2 deg. C

Rule #6: Any ECS measurements during a Perigee Passage that are cold MUST be assigned to the nominal

ECS run SI modes. i.e. Any requested Rawmode runs can be done with a warm focal plane.

All ECS SI mode possibilities are combined into 3 modes for the purposes of plotting.: TE_00C60 .

All of the TE_00CA8s get counted as TE_007AE

A word about the COLD Time stats:

Cold Time is defiined by focal plane temperatures <= -117.2 degrees C:

Nominal SI Mode Mapping between 6,5 and 4 chip modes:

The 6 chip SI Modes consist of three distinct modes. The 5 and 4 chip modes are mapped into the 6 chip modes in the following manner:

6 chip 5 chip 4 chip

TE_007AC -> TE_00C60 -> TE_00D78

TE_00B26 -> TE_00C60 -> TE_00D78

TE_007AE -> TE_00CA8 -> TE_00D78

TE_007AC, TE_007AE and TE_00B26

When an SI mode can be combined to more than one of the main three, its total time will be added to the mode with the least total time.

SI Mode to Chip Mappings:

TE_007AC -> I0 - I3, S2, S3

TE_007AE -> S0 - S5

TE_00B26 -> I0 - I3, S1, S3

TE_00C60 -> I0 - I3, S3

TE_00C62 -> I1 - I3, S3

TE_00CA8 -> S1 - S5

Back To Top